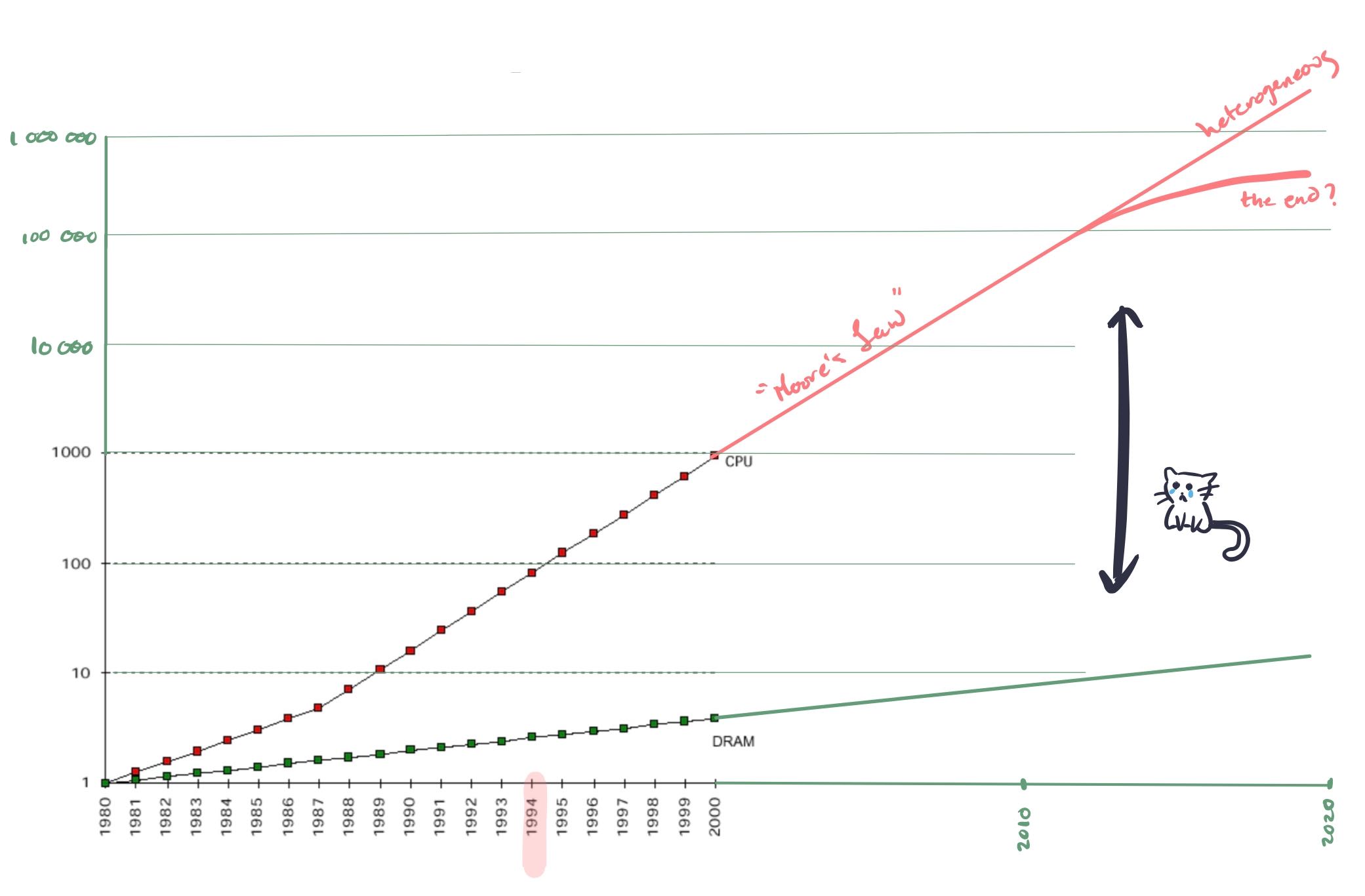

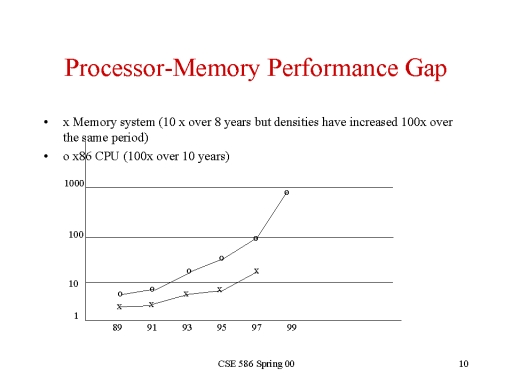

Reducing processor-memory performance gap and improving network-on-chip throughput | Semantic Scholar

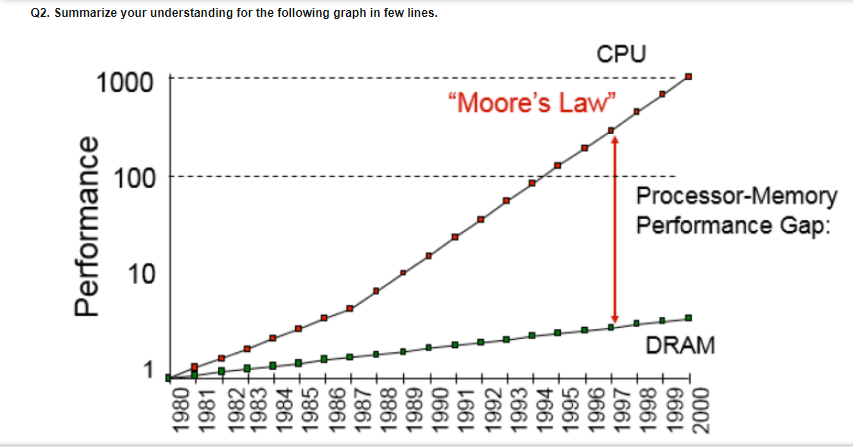

CPU-memory performance gap. Modelled after " Computer Architecture " :... | Download Scientific Diagram

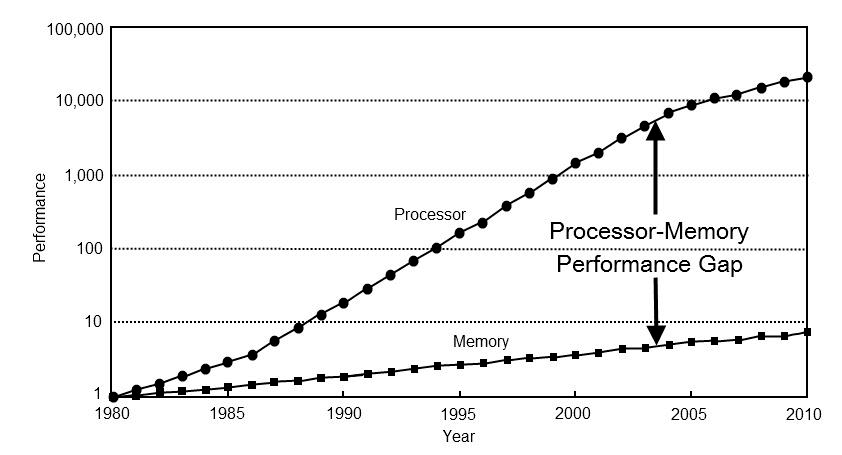

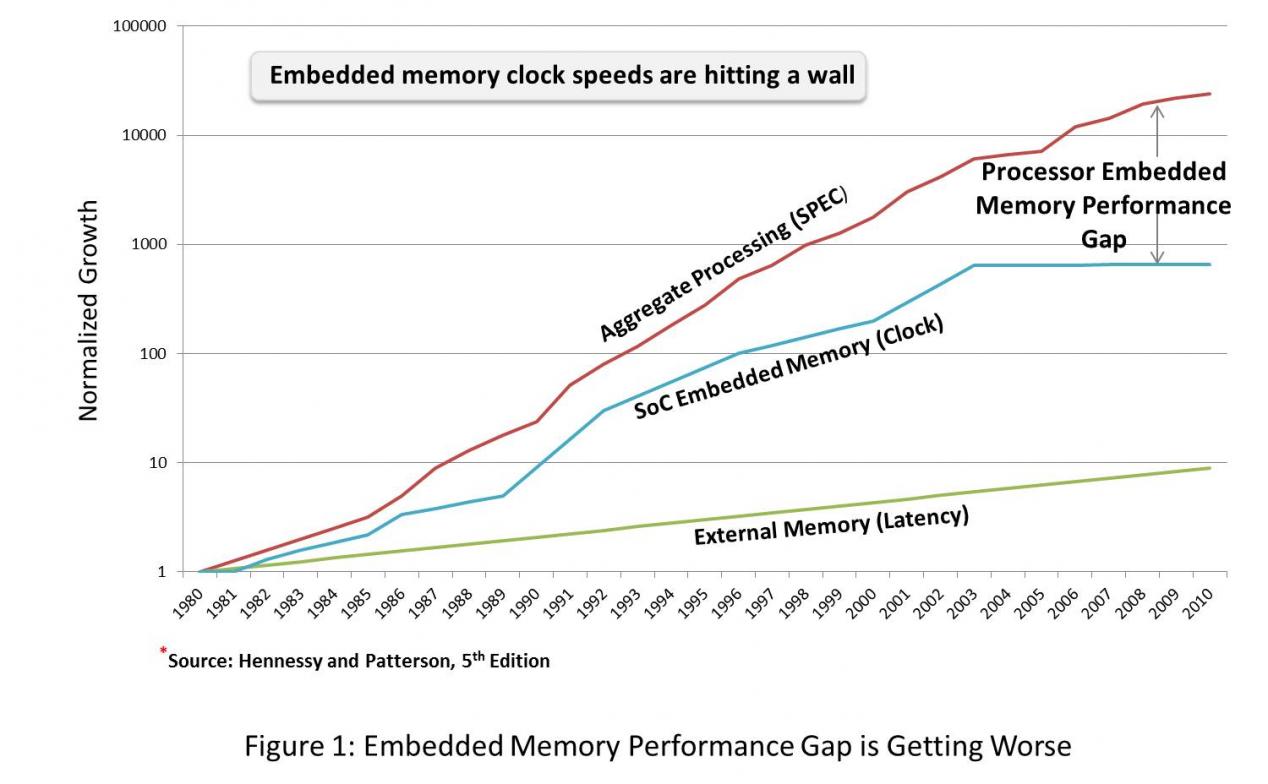

Figure 1 from A 1,000x improvement in computer systems by bridging the processor-memory gap | Semantic Scholar

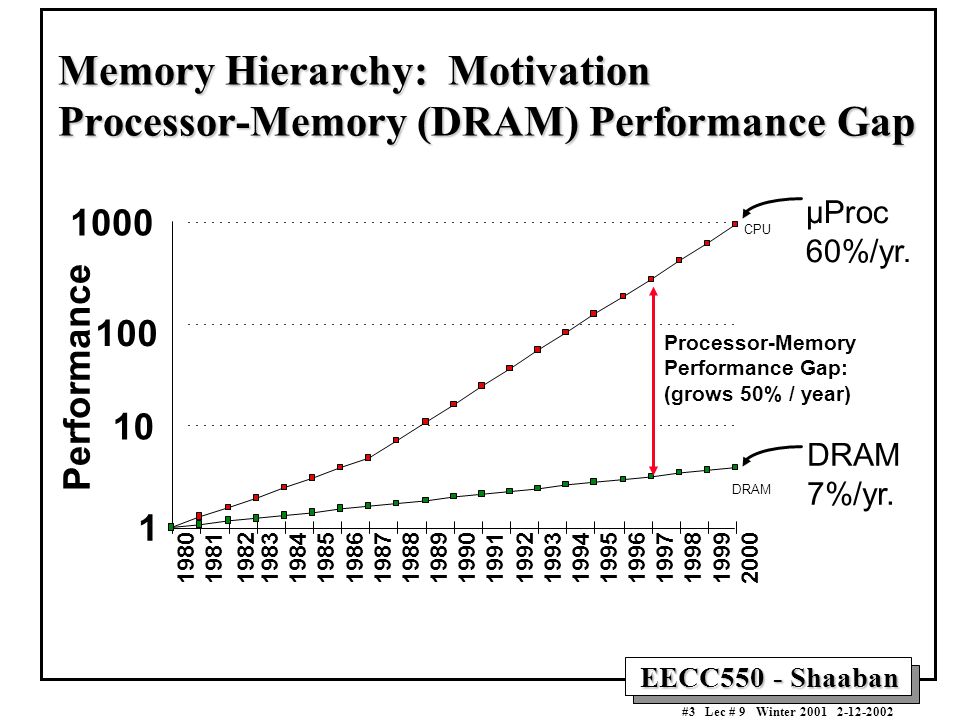

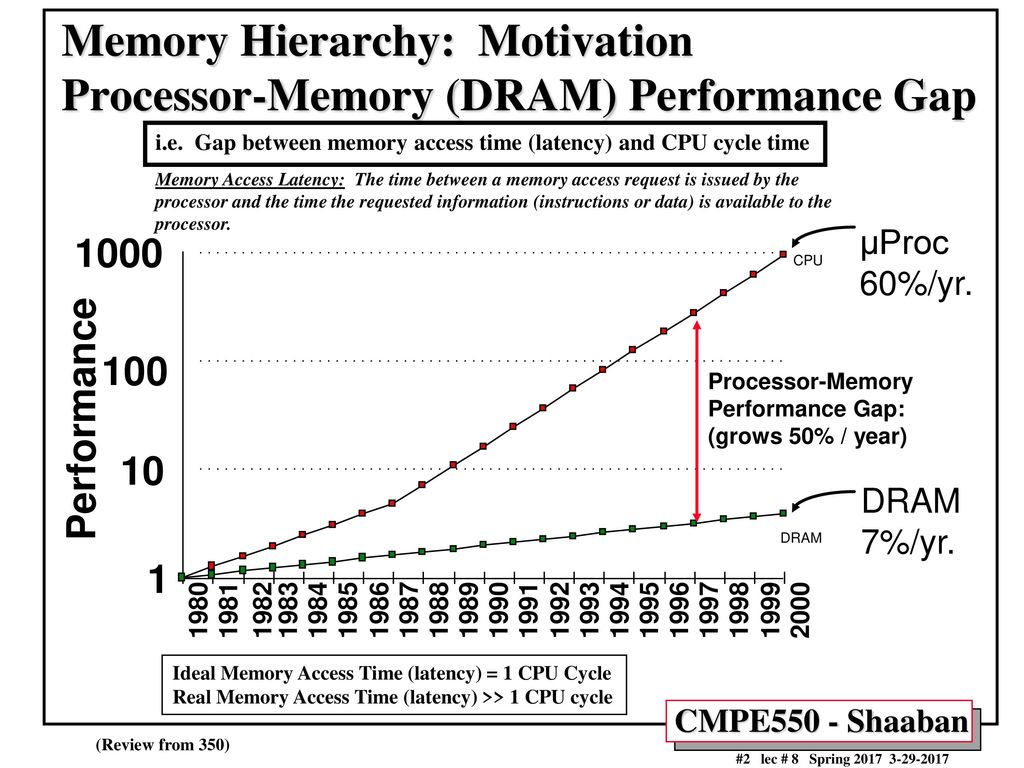

EECC550 - Shaaban #1 Lec # 9 Winter Memory Hierarchy: Motivation The gap between CPU performance and realistic (non-ideal) main memory speed. - ppt download

CPU-memory performance gap. Modelled after " Computer Architecture " :... | Download Scientific Diagram

![Processor-Memory Performance Gap.[Hen96]. | Download Scientific Diagram Processor-Memory Performance Gap.[Hen96]. | Download Scientific Diagram](https://www.researchgate.net/publication/2500537/figure/fig1/AS:646801187172353@1531220828934/Processor-Memory-Performance-GapHen96.png)

![Processor-Memory Performance Gap.[Hen96] . | Download Scientific Diagram Processor-Memory Performance Gap.[Hen96] . | Download Scientific Diagram](https://www.researchgate.net/publication/3214931/figure/fig1/AS:669980936921091@1536747311324/Processor-Memory-Performance-GapHen96.png)

![Processor-Memory Performance Gap.[Hen96] . | Download Scientific Diagram Processor-Memory Performance Gap.[Hen96] . | Download Scientific Diagram](https://www.researchgate.net/profile/Katherine-Yelick/publication/3214931/figure/fig1/AS:669980936921091@1536747311324/Processor-Memory-Performance-GapHen96_Q640.jpg)

![PDF] The Gap between Processor and Memory Speeds | Semantic Scholar PDF] The Gap between Processor and Memory Speeds | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6ebec8701893a6770eb0e19a0d4a732852c86256/3-Figure2-1.png)